# HSA6880 Single Channel Isolated Gate Driver with Protection

### **Features**

## 1 Features

- Single-channel isolated driver optimized for automotive and industrial applications

- 3.5A source and sink peak output currents

100V/ns operating common mode transient

- immunity

- Typical 90 ns propagation delay

- Less than ±30 ns pulse width distortion

- Integrated IGBT protection functions:

- IGBT soft shutdown (SSD)

- Desaturation detection (DESAT)

- Active Miller current clamp

- Input-side and output-side undervoltage lockout (UVLO) protection

- Fault sensing/reporting to the system controller (DESAT and UVLO)

- Dual complementary TTL compatible inputs

- Extended -40 °C to +125 °C temperature range

- Bipolar or unipolar supply operation

- Wide 30 V output supply range

- UL1577 certification and  $V_{ISO} = 3333 V_{RMS}$  for 60 seconds

- Automotive AECQ-100 Qualified Grade 1

# 2 Applications

- Automotive OBC and traction inverters

- AC/DC motor drives

- Air-conditioning inverters

- Welding/plasma equipment

- Uninterruptible power supplies

- Battery charging systems

- Auxiliary inverters for HEV and EV

- PV solar inverters and optimizers

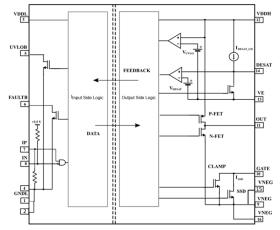

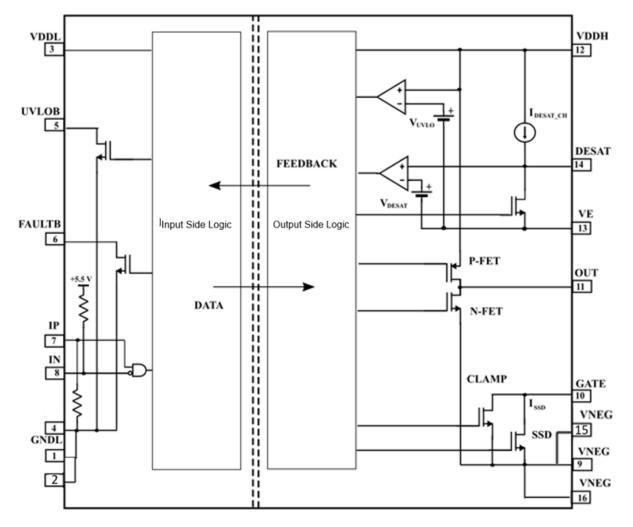

Figure 1 – HSA6880 functional block diagram

## 3 Description

The HSA6880 is a single channel isolated gate driver with complete protection features. It can be used for fast-switching drive and protection of power IGBTs, Si and SiC MOSFETs.The driver incorporates galvanically isolated technology to enable 3333  $V_{rms}$  input-to-output isolation voltage and high transient immunity (100 V/ns) as required in the industrial and automotive applications.

Its short propagation delay and small timingskew helps to achieve optimum performance at higher switching speeds when compared with other driver solutions available in the market. All logic pins are TTL compatible for easy interface to standard controllers and MCUs.

The HSA6880 architecture complete integrate protection features for protecting the devices in harsh environments. These integrated features include desaturation sensing with soft shutdown protection (also known as soft turn OFF), input-side and output-side undervoltage lockout (UVLO), active Miller current clamping and fault reporting.

The device supports bipolar and unipolar supply voltage configurations. In a bipolar configuration, the driver is typically supplied with voltages of +18V and -5V. For unipolar configuration, the driver is typically supplied with a positive 18 V (max 30 V).

The HSA6880 comes in a SOIC-16 wide-body package to meet UL isolation, creepage and clearance requirement.

# **Table of Contents**

| 1  | Features1                                    |            |                                           |   |  |  |  |  |

|----|----------------------------------------------|------------|-------------------------------------------|---|--|--|--|--|

| 2  | Appli                                        | cations    | 1                                         | I |  |  |  |  |

| 3  | Description1                                 |            |                                           |   |  |  |  |  |

| 4  | Pin Co                                       | onfigurati | on                                        | 3 |  |  |  |  |

| 5  | Speci                                        | fications. |                                           | 1 |  |  |  |  |

|    | 5.1                                          | Absolute   | maximum ratings                           | 1 |  |  |  |  |

|    | 5.2                                          | Electro-s  | tatic discharge                           | 1 |  |  |  |  |

|    | 5.3                                          | Recomm     | ended operating conditions                | 5 |  |  |  |  |

|    | 5.4                                          | Electrical | l characteristics                         | 5 |  |  |  |  |

|    |                                              | 5.4.1      | Power supply and UVLO timing              | 5 |  |  |  |  |

|    |                                              | 5.4.2      | Logic inputs and outputs                  | 3 |  |  |  |  |

|    |                                              | 5.4.3      | Gate Driver output characteristics        | 3 |  |  |  |  |

|    |                                              | 5.4.4      | Active Miller clamp and Soft Shutdown     | 7 |  |  |  |  |

|    |                                              | 5.4.5      | Desaturation protection                   | 7 |  |  |  |  |

|    |                                              | 5.4.6      | Insulation Specifications                 | 3 |  |  |  |  |

|    |                                              | 5.4.7      | Package characteristics                   | 3 |  |  |  |  |

| 6  | Detai                                        | led Descri | ption                                     | 3 |  |  |  |  |

|    | 6.1                                          | Power Su   | upplies                                   | 9 |  |  |  |  |

|    | 6.2                                          | Input and  | d Output                                  | ) |  |  |  |  |

|    |                                              | 6.2.1      | Non-Inverting and Inverting Inputs        | ) |  |  |  |  |

|    |                                              | 6.2.2      | Propagation delay and Rise and Fall Times | ) |  |  |  |  |

|    |                                              | 6.2.3      | FAULTB and UVLOB outputs10                | ) |  |  |  |  |

|    |                                              | 6.2.4      | Driver output10                           | ) |  |  |  |  |

|    | 6.3                                          | Internal   | UVLO protection10                         | ) |  |  |  |  |

|    |                                              | 6.3.1      | Normal UVLO10                             | ) |  |  |  |  |

|    |                                              | 6.3.2      | Short UVLO rejection11                    | 1 |  |  |  |  |

|    |                                              | 6.3.3      | Unstable VDDH recovery11                  | 1 |  |  |  |  |

|    | 6.4                                          | External   | Protection12                              | 2 |  |  |  |  |

|    |                                              | 6.4.1      | Desaturation Protection (DESAT)12         | 2 |  |  |  |  |

|    |                                              | 6.4.2      | Active Miller clamping                    | 1 |  |  |  |  |

| 7  | Isolat                                       | ion        |                                           | 1 |  |  |  |  |

| 8  | Comm                                         | non Mode   | e Transient Immunity1ង                    | 5 |  |  |  |  |

| 9  | Interl                                       | ock Prote  | ction15                                   | 5 |  |  |  |  |

| 10 | Recor                                        | nmended    | Application Circuit                       | 7 |  |  |  |  |

| 11 | Packa                                        | ge Outlin  | e Drawings18                              | 3 |  |  |  |  |

| 12 | Tape and Reel Dimensions, SOIC16 Wide-Body18 |            |                                           |   |  |  |  |  |

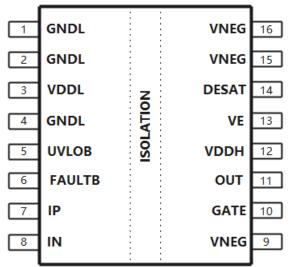

## 4 Pin Configuration

Figure 2 – HSA6880 pin configuration

| PIN | Name   | Description                                                                                   |

|-----|--------|-----------------------------------------------------------------------------------------------|

| 1   | GNDL   | Input-side ground                                                                             |

| 2   | GNDL   | Input-side ground                                                                             |

| 3   | VDDL   | Input-side power supply                                                                       |

| 4   | GNDL   | Input-side ground                                                                             |

| 5   | UVLOB  | Under-voltage lockout, open drain active LOW output                                           |

| 6   | FAULTB | Desaturation protection fault, open drain active LOW output                                   |

| 7   | IP     | Non-inverting driver input <sup>1</sup> . On-chip 120 k $\Omega$ pull-down to GNDL            |

| 8   | IN     | Inverting driver input <sup>2</sup> . On-chip 120 k $\Omega$ pull-up to internal 5.5 V supply |

| 9   | VNEG   | Output-side negative supply voltage                                                           |

| 10  | GATE   | IGBT Gate connection for Miller current clamp and SSD (soft shutdown)                         |

| 11  | OUT    | Driver output                                                                                 |

| 12  | VDDH   | Output-side positive supply                                                                   |

| 13  | VE     | Supply reference for VDDH and VNEG, connected to IGBT emitter                                 |

| 14  | DESAT  | Desaturation (overcurrent protection) sensing input                                           |

| 15  | VNEG   | Output-side negative supply voltage                                                           |

| 16  | VNEG   | Output-side negative supply voltage                                                           |

Notes:

1) IP pin controls the IGBT driver output (OUT pin) when IN pin is set to LOW. The IGBT driver is turned ON if IP pin is set to HIGH and IN pin is set to LOW, otherwise, the IGBT driver OUT pin is turned OFF. A minimum pulse width is required to suppress glitches while controlling the IGBT driver. An internal pull-down resistor ensures that the IGBT driver is kept in OFF-state if IP pin is left unconnected.

2) IN pin controls the IGBT driver OUT pin when IP pin is set to HIGH. The IGBT driver is turned ON if IN pin is set to LOW, and is turned OFF if IN pin is set to HIGH. An internal pull-up resistor ensures that the IGBT driver is kept in OFF-state if IN pin is left unconnected.

| Device Information      |         |                    |               |                |            |  |  |  |

|-------------------------|---------|--------------------|---------------|----------------|------------|--|--|--|

| PART NUMBER PACKAGE BOD |         | BODY SIZE          | TAPE AND REEL | Device Marking | Comment    |  |  |  |

| HSA6880WSRS             | SOIC-16 | 10.30 mm × 7.50 mm | Reel          | HSA6880-S      | Industrial |  |  |  |

| HSA6880WSRQ             | SOIC-16 | 10.30 mm × 7.50 mm | Reel          | HSA6880-Q      | Automotive |  |  |  |

# 5 Specifications

## 5.1 Absolute maximum ratings

Absolute maximum ratings are defined as ratings, which if exceeded, may lead to the destruction of the integrated circuit. Unless otherwise specified, all voltages for input-side and output-side reference to GNDL pin and VE pin respectively.

| Parameter                                            | Symbol             | Min      | Max      | Unit |

|------------------------------------------------------|--------------------|----------|----------|------|

| Input-side supply voltage                            | VDDL               | -0.3     | 30       | V    |

| Output-side positive supply voltage                  | VDDH               | -0.3     | 30       | V    |

| Output-side negative supply voltage                  | VNEG               | -15      | 0.3      | V    |

| Output-side total bipolar supply voltage (VDDH-VNEG) | Vmax_out           |          | 30       | V    |

| OUT voltage                                          | Vout               | VNEG-0.3 | VDDH+0.3 | V    |

| OUT peak source current <sup>1</sup>                 | IOUT_SOURCE        | /        | 7        | А    |

| OUT peak sink current <sup>2</sup>                   | IOUT_SINK          | /        | 7        | А    |

| GATE clamping sink current <sup>3</sup>              | ICLAMP_SINK        | /        | 2.5      | А    |

| Input-side logic levels (UVLOB, FAULTB)              | VLOGIC             | -0.3     | 5.5      | V    |

| Non-inverting driver input voltage                   | VIP                | -0.3     | 5.5      | V    |

| Inverting driver input voltage                       | Vin                | -0.3     | 5.5      | V    |

| DESAT voltage                                        | V <sub>DESAT</sub> | -0.3     | VDDH+0.3 | V    |

| GATE voltage                                         | Vclamp             | VNEG-0.3 | VDDH+0.3 | V    |

| Junction temperature                                 | TJ                 | -40      | 150      | °C   |

| Storage temperature                                  | T <sub>STG</sub>   | -55      | 150      | °C   |

| Operating temperature                                | T <sub>A</sub>     | -40      | 125      | °C   |

| Input-side power dissipation <sup>4</sup>            | P <sub>D_IN</sub>  |          | 150      | mW   |

| Output-side power dissipation <sup>4</sup>           | Pd_out             |          | 520      | mW   |

Note:

1) The OUT peak current is measured at maximum pulse width equal to 2.5 µs, maximum duty cycle 1%.

2) The OUT sink current is measured at maximum OFF time equal to 2.5 µs, maximum duty cycle 99%.

3) The GATE clamp sink current is measured at maximum OFF time equal to 2.5 μs, maximum duty cycle 99% and voltage between GATE pin and VNEG pin equal to 2 V.

4) Output IC power dissipation is derated linearly above 100°C from 520 mW to 260 mW at 125°C.

## 5.2 Electro-static discharge

| Parameter                  | Symbol   | Min | Max  | Unit |

|----------------------------|----------|-----|------|------|

| ESD – Human Body Model     | Vesd_hbm | /   | 4.0  | kV   |

| ESD – Charged Device Model | Vesd_cdm | /   | 1000 | V    |

## 5.3 Recommended operating conditions

| Parameter                                | Symbol    | Min | TYP | Max | Unit |

|------------------------------------------|-----------|-----|-----|-----|------|

| Input-side supply voltage                | VDDL      | 8   | 12  | 18  | V    |

| Output-side positive supply voltage      | VDDH-VE   | 14  | -   | 28  | V    |

| Output-side negative supply voltage      | VNEG-VE   | -12 | -   | 0   | V    |

| Output-side total bipolar supply voltage | VDDH-VNEG | -   | -   | 28  | V    |

| Ambient operating temperature            | TA        | -40 | -   | 125 | °C   |

| Input pulse width <sup>1</sup>           | ton       | 250 | -   | -   | ns   |

| Noto                                     |           |     |     |     |      |

Note:

1) Tested with a load of 10 nF capacitor and a 10  $\Omega$  resistor in series.

## 5.4 Electrical characteristics

Unless otherwise specified, all MIN/MAX specification parameters are over the recommended operating conditions, all voltages at input-side are referenced to GNDL pin. All voltages at output-side are referenced to VNEG pin. All typical values are tested at  $T_A = 25$  °C, VDDL = 12 V, VDDH-VNEG = 20 V, VE-VNEG = 0 V.

### 5.4.1 Power supply and UVLO timing

| Parameters                                             | Symbol                   | MIN  | ТҮР  | MAX  | Unit |

|--------------------------------------------------------|--------------------------|------|------|------|------|

| Input-side current (driver OFF)                        | LS_OFF                   |      | 3.6  | 6.0  | mA   |

| Input-side current (driver ON)                         | Ils_on                   |      | 11.4 | 14.5 | mA   |

| Output-side current (driver OFF)                       | HS_OFF                   |      | 6.8  | 10   | mA   |

| Output-side current (driver ON)                        | HS_ON                    |      | 7.5  | 11   | mA   |

| VDDH UVLO threshold voltage (ON) <sup>1</sup>          | VDDHUVLO_H               | 11.2 | 12.2 | 13.2 | V    |

| VDDH UVLO threshold voltage (OFF) <sup>1</sup>         | VDDH <sub>UVLO_L</sub>   | 10.5 | 11.5 | 12.5 | V    |

| VDDH UVLO hysteresis <sup>1</sup>                      | VDDH <sub>UVLO_HYS</sub> |      | 0.7  |      | V    |

| VDDL UVLO threshold voltage (ON) <sup>1</sup>          | VDDL <sub>UVLO_H</sub>   |      | 7.5  |      | V    |

| VDDL UVLO threshold voltage (OFF) <sup>1</sup>         | VDDL <sub>UVLO_L</sub>   |      | 7.3  |      | V    |

| VDDL UVLO hysteresis <sup>1</sup>                      | VDDL <sub>UVLO_HYS</sub> |      | 0.2  |      | V    |

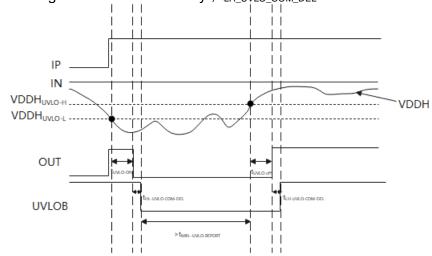

| Minimum duration for UVLOB LOW report <sup>2</sup>     | tmin_uvlo_report         |      | 100  |      | μs   |

| VDDH UVLO to OUT go low delay <sup>2</sup>             | tuvlo_on                 |      | 8.8  |      | μs   |

| VDDH UVLO to OUT go high delay <sup>2</sup>            | tuvlo_off                |      | 8.8  |      | μs   |

| OUT to UVLOB high low                                  | 4                        |      | 1.1  |      |      |

| communication delay <sup>2</sup>                       | thl_uvlo_com_del         |      | 1.1  |      | μs   |

| OUT to UVLOB low high communication delay <sup>2</sup> | tlh_uvlo_com_del         |      | 1.1  |      | μs   |

Notes:

1) UVLO is measured with respect to VDDH - VE.

2) Guaranteed by design. (See Figure 4 to Figure 6 for definition of timing.)

### 5.4.2 Logic inputs and outputs

Test conditions: All typical values at  $T_A = 25$ °C; VDDL-GNDL = 12 V; VDDH-VE = 20 V; VNEG-VE = 0 V; -40°C <  $T_A$  < 125°C.

| Parameters                                       | Symbol               | MIN | ТҮР | MAX | Unit |

|--------------------------------------------------|----------------------|-----|-----|-----|------|

| IN current (HIGH = 5 V)                          | Ііл_н                |     | 0   |     | μA   |

| IP current (HIGH = 5 V)                          | I <sub>IP_H</sub>    |     | 45  |     | μA   |

| IN current (LOW = 0 V)                           | I <sub>IN_L</sub>    |     | -50 |     | μA   |

| IP current (LOW = 0 V)                           | I <sub>IP_L</sub>    |     | 0   |     | μA   |

| IN voltage (LOW)                                 | V <sub>IN_L</sub>    |     |     | 0.8 | V    |

| IN voltage (HIGH)                                | V <sub>IN_H</sub>    | 2.4 |     |     | V    |

| IP voltage (LOW)                                 | VIP_L                |     |     | 0.8 | V    |

| IP voltage (HIGH)                                | VIP_H                | 2.4 |     |     | V    |

| FAULTB, UVLOB current (LOW = 0 V)                | I <sub>DIG_LOW</sub> |     |     | 10  | mA   |

| Voltage of UVLOB (FAULTB) pin when sinking 10 mA | V <sub>DIG_LOW</sub> |     |     | 400 | mV   |

### 5.4.3 Gate Driver output characteristics

Test conditions: All typical values at  $T_A = 25^{\circ}C$ ; VDDL-GNDL = 12 V; VDDH-VE = 20 V; VNEG-VE = 0 V;  $C_L = 100 \text{ pF}$ ; -40°C <  $T_A < 125^{\circ}C$ .

| Parameters                                               | Symbol                | Conditions                                                               | MIN | TYP      | MAX | Unit |

|----------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|-----|----------|-----|------|

| High level output voltage                                | Vout_h                | loυτ = -100 mA                                                           |     | VDDH-0.2 |     | V    |

| Low level output voltage                                 | Vout_l                | l <sub>ουτ</sub> = 100 mA                                                |     | VNEG+0.1 |     | V    |

| Peak source output current                               | IOUT_SOURCE           | V <sub>OUT</sub> =V <sub>DDH</sub> –18V<br>C∟=10nF<br>Single Pulse = 1us | 3.5 | 5.5      |     | A    |

| Peak sink output current                                 | I <sub>OUT_SINK</sub> | $V_{OUT}=V_{NEG}+18V$<br>$C_L=10nF$<br>Single Pulse = 1us                | 3.5 | 5.5      |     | А    |

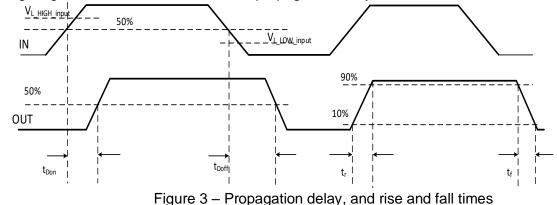

| Output voltage rise time (10 % to 90%)                   | tr                    | Rg=10 Ω, C∟= 10 nF                                                       |     | 42       |     | ns   |

| Output voltage fall time (90% to10%)                     | tr                    | Rg=10 Ω, C∟= 10 nF                                                       |     | 32       |     | ns   |

| Turn ON propagation delay (50% to 50%)                   | t <sub>D_ON</sub>     | Rg=10 Ω, C∟= 10 nF                                                       |     | 90       |     | ns   |

| Turn OFF propagation delay (50% to 50%)                  | t <sub>D_OFF</sub>    | Rg=10 Ω, C∟= 10 nF                                                       |     | 90       |     | ns   |

| Pulse width distortion <sup>1</sup>                      | PWD                   | Guaranteed by design                                                     |     | ±30      |     | ns   |

| Dead-time distortion <sup>2</sup>                        | DTD                   | Guaranteed by design                                                     |     | ±40      |     | ns   |

| Common mode transient immunity Logic High <sup>3</sup>   | CMTI_LH               |                                                                          | 100 |          |     | V/ns |

| Common mode transient<br>immunity Logic Low <sup>3</sup> | CMTI_LL               |                                                                          | 100 |          |     | V/ns |

Notes:

1) Pulse width distortion (PWD) is defined as  $(t_{D_ON} - t_{D_OFF})$  in any given unit.

2) Deadtime Distortion (DTD) is defined as  $(t_{D_OFF} - t_{D_ON})$  between any two parts under the same test conditions. 3)  $V_{CM} = 1200 \text{ V}.$

### 5.4.4 Active Miller clamp and Soft Shutdown

Test conditions: All typical values at  $T_A = 25^{\circ}C$ ; VDDL-GNDL = 12 V; VDDH-VE = 20 V; VNEG-VE = 0 V;  $C_L = 100 \text{ pF}$ ; -40°C <  $T_A < 125^{\circ}C$ .

| Parameters                                                                | Symbol           | MIN | TYP        | MAX | Unit |

|---------------------------------------------------------------------------|------------------|-----|------------|-----|------|

| Soft shutdown (SSD) current during<br>fault conditions<br>VGATE–VNEG = 9V | Issd             |     | 50         |     | mA   |

| Clamp threshold voltage                                                   | $V_{CLP_TH}$     |     | VNEG+2.0   |     | V    |

| GATE clamp sink current <sup>1</sup>                                      | I <sub>CLP</sub> |     | 2.0        |     | А    |

| GATE clamp voltage <sup>2</sup>                                           | V <sub>CLP</sub> |     | VNEG + 0.3 |     | V    |

Notes:

1) The GATE clamp sink current is measured at  $V_{out} = VE + 3 V$ .

2) The voltage is measured at  $I_{CLP} = 100 \text{ mA}$ .

#### 5.4.5 Desaturation protection

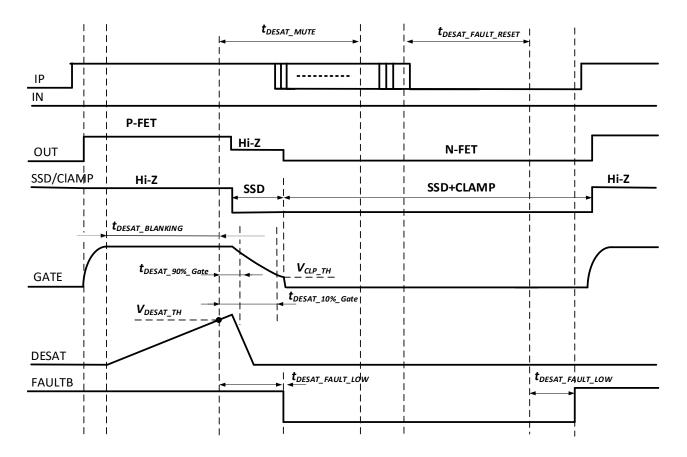

Test conditions: All typical values at  $T_A = 25$ °C; VDDL-GNDL = 12 V; VDDH-VE = 20 V; VNEG-VE = 0 V; C<sub>L</sub> = 100 pF; -40°C <  $T_A$  < 125°C (see Figure 9).

| Parameters                                  | Symbol                          | MIN | ТҮР | MAX | Test<br>Conditions               | Unit |

|---------------------------------------------|---------------------------------|-----|-----|-----|----------------------------------|------|

| DESAT threshold voltage                     | Vdesat_th                       | 6.5 | 7.1 | 7.6 |                                  | V    |

| DESAT charging current                      | IDESAT_CH                       |     | 0.9 |     | $V_{DESAT} = 2 V$                | mA   |

| DESAT discharging current                   | IDESAT_DSCH                     |     | 110 |     | $V_{\text{DESAT}} = 5 \text{ V}$ | mA   |

| Initial DESAT blanking time <sup>1, 2</sup> | t <sub>desat_blanki</sub><br>Ng |     | 0.5 |     | Guaranteed by<br>design          | μs   |

| DESAT output mute time <sup>1, 2</sup>      | tdesat_mute                     |     | 3.2 |     | Guaranteed by<br>design          | ms   |

| DESAT to FAULTB low delay <sup>1</sup>      | tdesat_faultb<br>_LOW           |     | 4.8 | 7   | Guaranteed by<br>design          | μs   |

| DESAT to 90% GATE delay <sup>1</sup>        | tdesat_90%_ga<br>TE             |     | 0.3 |     | $C_{\text{GATE}} = 1 \text{ nF}$ | μs   |

| DESAT to 10% GATE delay <sup>1</sup>        | tdesat_10%_ga<br>TE             |     | 0.8 |     | $C_{\text{GATE}} = 1 \text{ nF}$ | μs   |

| Off time to reset FAULTB <sup>1, 2</sup>    | tdesat_faultb<br>_reset         |     | 3.2 |     | Guaranteed by<br>design          | ms   |

Notes:

1) See Figure 9 for the DESAT parameters

2) Timing guaranteed by design depends on the clock frequency and can vary ±30%.

### 5.4.6 Insulation Specifications

| Parameters                                          | Symbol  | Conditions                                                        | Value | Unit |

|-----------------------------------------------------|---------|-------------------------------------------------------------------|-------|------|

| External clearance                                  | CLR     | Shortest terminal-to-terminal distance through air                | 8.3   | mm   |

| External creepage                                   | CPG     | Shortest terminal-to-terminal distance across the package surface | 8.3   | mm   |

| Distance through the insulation                     | DTI     | Minimum internal gap (Internal<br>clearance) of the insulation    | >17   | μm   |

| Insulation withstand voltage for 1 min <sup>1</sup> | Viso    |                                                                   | 3333  | Vrms |

| Insulation withstand voltage for 1 sec <sup>1</sup> | VISO_1s |                                                                   | 4000  | Vrms |

| Material Group                                      | MG      |                                                                   | _     |      |

| Pollution degree                                    |         |                                                                   | 2     |      |

Note:

1) The driver is treated according UL1577 (Pin 1 through pin 8 are shorted together and pin 9 through pin 16 are shorted together to form a two-terminal device).

#### 5.4.7 Package characteristics

| Parameters                                          | Symbol  | MIN | TYP              | MAX | Unit |

|-----------------------------------------------------|---------|-----|------------------|-----|------|

| Input-side to output-side resistance <sup>1</sup>   | RIN_OUT |     | 10 <sup>12</sup> |     | Ω    |

| Input-side to output-side capacitance <sup>1,</sup> | CIN_OUT |     | 1                |     | pF   |

| Junction to case thermal resistance                 | ЭгӨ     |     | 40               |     | °C/W |

| Junction to ambient thermal resistance              | ΘJA     |     | 75               |     | °C/W |

Notes:

1) The IGBT driver is treated as a two-terminal device. Pin 1 through pin 8 are shorted together and pin 9 through pin 16 are shorted together and  $V_{IO} = 500 \text{ V}$ .

2) f = 1 MHz

## 6 Detailed Description

HSA6880 is a single channel, galvanically-isolated, 3.5 A/1200 V IGBT driver in a SOIC16 Wide-Body package. It can be used for the fast switching of power IGBTs, Si and SiC MOSFETs. Basic galvanic isolation is provided on the chip. The HSA6880 architecture includes several control features which protect the IGBT in harsh industrial and automotive environments. These integrated features include IGBT desaturation sensing with soft turn OFF protection, Input-side and output-side under-voltage lockout (UVLO), active Miller current clamping and fault reporting to the system controller.

## 6.1 **Power Supplies**

Separate power supplies are required for the input-side and output-side due to the input and output of the HSA6880 being galvanically isolated from each other. The input-side power supply is connected to VDDL pin and GNDL pin. The supply voltage can be between 8 and 18 V. The IGBT driver supports bipolar and unipolar supply voltage configurations. For unipolar configuration, VE and VNEG pins are shorted. The IGBT driver is typically supplied by a positive 18 V (max 30 V). In a bipolar configuration, the driver is typically supplied with voltages of VDDH = +18 V, VNEG = -5 V, both with respect to VE.

## 6.2 Input and Output

### 6.2.1 Non-Inverting and Inverting Inputs

There are two possible input modes to control an IGBT driver:

1) Non-inverting mode (IP controls the driver output while IN is set to low).

2) Inverting mode (IN controls the driver output while IP is set to high).

A minimum input pulse width is defined to filter occasional glitches. Any glitch on IP or IN shorter than 40 ns would be ignored.

The truth table for input and output signals is shown below:

| IP | IN | OUT |

|----|----|-----|

| 0  | 0  | 0   |

| 0  | 1  | 0   |

| 1  | 0  | 1   |

| 1  | 1  | 0   |

### 6.2.2 Propagation delay and Rise and Fall Times

The timing diagram for rise and fall times and propagation delay are shown below.

#### 6.2.3 FAULTB and UVLOB outputs

The device has open-drain FAULTB and UVLOB outputs. When the DESAT fault control scheme reports overcurrent conditions of the IGBT, the FAULTB pin transitions from HIGH to LOW. The UVLOB pin transitions to LOW when an UVLO event occurs at the output-side power supply. Pull-up resistors are required on both pins (see Figure 17).

### 6.2.4 Driver output

The driver output section provides a rail-to-rail output, it clamps LOW during faults and under-voltage lockout. During normal operation condition, OUT pin drives the IGBT gate to HIGH or LOW according to the signals applied to IP pin and IN pin. The driver can provide up to 3.5 A sink and source peak currents to charge and discharge the IGBT gate capacitance.

## 6.3 Internal UVLO protection

To ensure correct switching of the power devices, an under-voltage lockout (UVLO) function is integrated in the output-side of the IGBT driver. When the output-side power supply, VDDH falls below VDDH<sub>UVLO\_L</sub>, the IGBT is turned OFF and the input signals at IP pin and IN pin are ignored until VDDH rises above VDDH<sub>UVLO\_H</sub>. The time between UVLO detection until the driver output goes low is "VDDH UVLO to OUT go low delay", t<sub>UVLO\_ON</sub>. The driver does not turn ON immediately when VDDH rises above VDDH<sub>UVLO\_H</sub>. The time between this event and the turn ON event is called "VDDH UVLO to OUT go high delay", t<sub>UVLO\_OFF</sub>.

#### 6.3.1 Normal UVLO

When an UVLO event happens, a report is sent to the UVLOB pin. The time between the driver output going low to the time UVLOB pin goes low is "OUT to UVLOB high low communication delay",  $t_{HL_UVLO_COM_DEL}$ . The time between the driver output going high to the time UVLOB pin goes high is "OUT to UVLOB low high communication delay",  $t_{LH_UVLO_COM_DEL}$ .

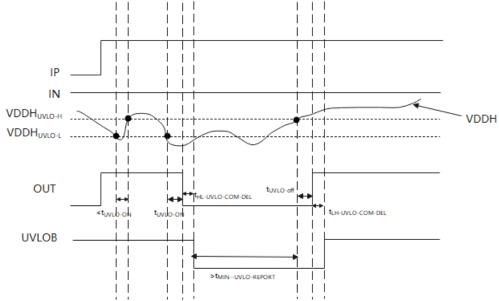

Figure 4 – the HSA6880 during UVLO condition for times higher than t<sub>MIN\_UVLO\_REPORT</sub>.

### 6.3.2 Short UVLO rejection

When VDDH falls below the threshold voltage VDDH<sub>UVLO\_L</sub> for a time shorter than the time  $t_{UVLO_ON}$ , the driver does not turn OFF as shown in

When UVLOB pin is reported and VDDH rises above VDDH<sub>UVLO\_H</sub>, the driver is enabled, and OUT pin goes high only after time  $t_{UVLO_OFF}$ . The UVLO pin goes high after the  $t_{MIN_UVLO_REPORT}$  time and communication delay,  $t_{HL_UVLO_COM_DEL}$ .

Figure 5 – Short UVLO rejection

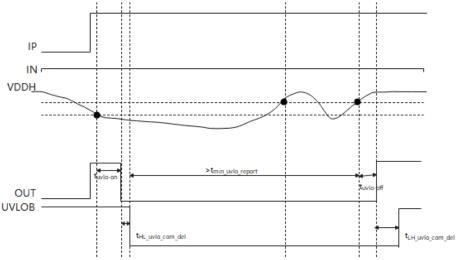

### 6.3.3 Unstable VDDH recovery

When the driver is under UVLO condition and VDDH goes high but is not stable, the driver output will not go high until VDDH rises above VDDH<sub>UVLO\_H</sub> for a time longer than  $t_{UVLO_OFF}$ . This is shown in Figure 6.

Figure 6 – Unstable VDDH recovery

### 6.4 External Protection

### 6.4.1 Desaturation Protection (DESAT)

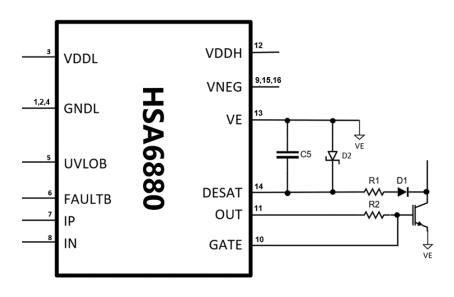

The IGBT driver has a DESAT pin for de-saturation protection which monitors the IGBT collector emitter saturation voltage ( $V_{CE}$ ). The DESAT pin is connected to the IGBT collector by a diode, D1, and a resistor R1. The diode blocks the voltage across the IGBT during its OFF state. The diode should be fast to respond to the fault and has minimum reverse recovery to prevent a false trip. For very high IGBT blocking voltages in the kilovolts range, multiple diodes in series could be used. Multiple diodes can also be used to adjust the actual DESAT threshold voltage.

$$V_{DESAT_TH_ACTUAL} = V_{DESAT_TH} - I_{DESAT_{CH}} * R_1 - n * V_F$$

Where n is number of diodes and  $V_F$  is a diode forward voltage drop. The time for the driver to respond to DESAT condition is known as blanking time,  $t_{DESAT\_BLANKING}$ . The blanking time depends on the internal charge current,  $I_{DESAT\_CH}$ , DESAT reference threshold voltage,  $V_{DESAT\_TH}$ , and the DESAT capacitor, C5 (see Figure 7). C5 starts to charge with current  $I_{DESAT\_CH}$ . A zener diode, D2, is placed in parallel with the capacitor C5 to avoid any voltage overshoot between DESAT and VE pins.

When the voltage on DESAT pin becomes higher than V<sub>DESAT\_TH</sub>, soft turn OFF of the IGBT is performed. The capacitor value determines the blanking time t<sub>DESAT\_BLANKING</sub>.

Figure 7 – DESAT circuitry

Figure 8 – HSA6880 functional block diagram

The driver time diagram during DESAT conditions is shown in Figure 10. The delay from DESAT sense to starting soft turn OFF is less than 40 ns (typical). The driver input is muted (ignored) for a minimum time,  $t_{DESAT\_MUTE}$ , which typical value is 3.2 ms. After the muting time has expired, the driver input is expected to stay continuously low for a minimum DESAT fault reset time,  $t_{DESAT\_FAULTB\_RESET}$ , which typical value is 3.2 ms. Depend on the driver input, there are three cases when  $t_{DESAT\_FAULTB\_RESET}$  will start:

- If the driver input is low at the end of the muting time, *t*<sub>DESAT\_FAULTB\_RESET</sub> starts immediately;

- If the driver input is high at the end of the muting time, *t*<sub>DESAT\_FAULTB\_RESET</sub> is started as soon as the input goes low;

- If the driver input toggles high/low during *t*<sub>DESAT\_FAULTB\_RESET</sub>, then t<sub>DESAT\_FAULTB\_RESET</sub> is restarted every time the driver input goes low.

The time to discharge the GATE depends on the IGBT input capacitance, gate-source and drainsource voltages, and the soft-shutdown current during fault conditions ( $I_{SSD}$ ), which is typically 50 mA. When the GATE voltage drops to  $V_{CLP\_TH}$ , the IGBT gate is shorted to VNEG through the following FETs: CLAMP, main N-FET and SSD. When desaturation protection is activated, the FAULTB pin on the input-side goes to LOW. The time from the DESAT sense is detected and setting the FAULTB pin to LOW,  $t_{DESAT\_FAULTB\_LOW}$ , is 7µs (Max) by design.

Figure 9 – Driver time diagram during DESAT conditions (the timescale is not proportional)

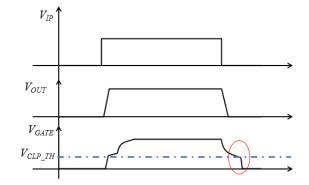

#### 6.4.2 Active Miller clamping

When the IGBT is turned off and the gate voltage drops to the Miller clamp threshold voltage,  $V_{CLP_TH}$ , the GATE pin goes from Hi-Z to driving LOW.

## 7 Isolation

The galvanically isolated barrier in the IGBT driver electrically isolates circuitry between the input-side and the output-side. This barrier prevents unwanted AC or DC signals from traveling from one side to the other.

# 8 Common Mode Transient Immunity

Common mode transient immunity (CMTI) is a key specification parameter of isolated drivers. CMTI is the maximum tolerable rate of the rise or fall of the common mode voltage, V<sub>CM</sub>. HSA6880 is implemented in an advanced Silicon-on-Insulator high-voltage process (SOI) which allows the driver to operate latch-up free (by design), even in the presence of large over/under-shoot voltage excursions. The SOI process allows galvanic separation of internal NFET and PFET devices, preventing the formation of parasitic BJT or thyristors which are the main cause of circuit latch-up. As a result, the driver is immune to the noise generated by large dv/dt and di/dt variations during IGBTs or SiC MOSFETs switching.

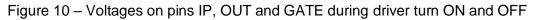

## 9 Interlock Protection

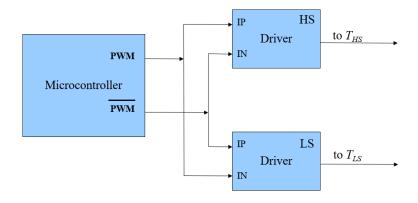

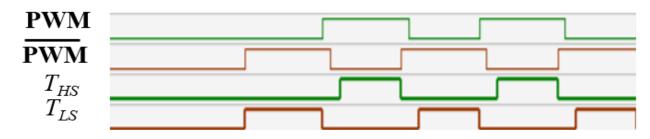

The HSA6880 integrates a DEAD-TIME block as an interlock protection function to protect from undesired shoot-through operation. Figure 11 shows the HSA6880 digital top block diagram.

Figure 11 – HSA6880 digital top block diagram

IGBTs are mostly used in three-phase applications such as variable-frequency drives, uninterruptible power supplies, solar inverters, and other similar inverter applications. To ensure proper operation of an inverter, the switches of the inverter leg should not switch simultaneously. A dead-time period is inserted before the transition of output-side and input-side switches to avoid shoot-through.

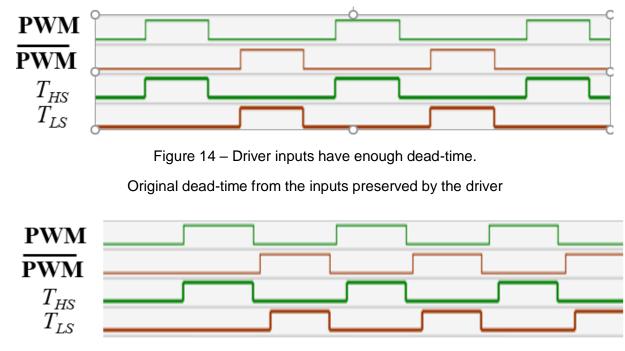

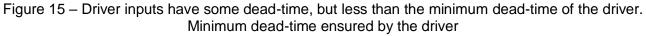

Figure 13 shows one leg of three-phase converter. Each IGBT has its own driver. When the drivers are connected according to Figure 14, a minimum dead-time of 0.8  $\mu$ s will be introduced before the switches change state. This feature prevents a shoot-through condition.

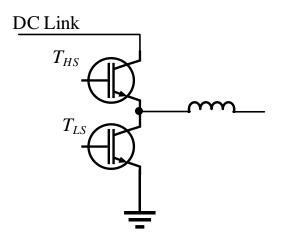

Figure 12 – A leg of three-phase inverter

Figure 13 – High and low side drivers connection for interlock protection

Three examples are shown below:

Figure 16 – Driver inputs overlapping.

Minimum dead-time ensured by the driver

# **10 Recommended Application Circuit**

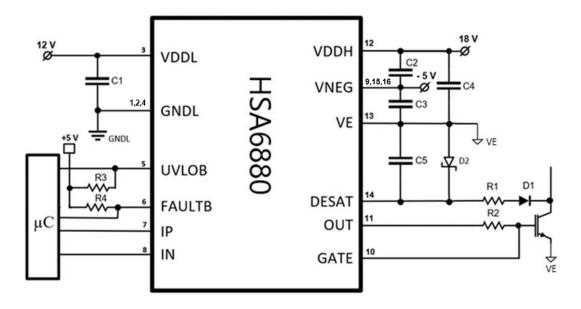

Figure 17 shows a recommended application circuit for the IGBT driver.

Figure 17 – HSA6880 recommended application circuit

Capacitors C1 and C2 are the decoupling capacitors (recommended value = 1  $\mu$ F). Capacitors C3 and C4 are decoupling capacitors (recommended value = 10  $\mu$ F). The DESAT circuit includes a high voltage diode (D1), a 1 k $\Omega$  resistor (R1) and 220 pF capacitor (C5). Diode (D2) prevents the voltage on the DESAT pin from falling 0.4 V below the voltage on VE pin.

The gate resistor (R2) limits the gate charge current and indirectly controls the IGBT collector voltage. Its value depends on the IGBT type. A recommended value is 5  $\Omega$ .

The pull-up resistors (R3, R4) ensure the input-side outputs are HIGH when no faults are detected. Their recommended value is  $3.3 \text{ k}\Omega$ .

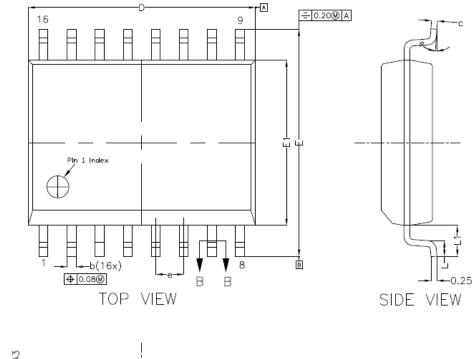

## **11 Package Outline Drawings**

The HSA6880 uses a SOIC16 Wide-Body package as shown below:

<sup>\*</sup> CONTROLLING DIMENSION : MM

| SYMBOL | MILLIMETER |       |       |  |  |  |

|--------|------------|-------|-------|--|--|--|

|        | MIN.       | NOM.  | MAX.  |  |  |  |

| А      |            |       | 2.65  |  |  |  |

| A1     | 0.10       |       | 030   |  |  |  |

| A2     | 2.25       | 2.30  | 2.35  |  |  |  |

| A3     | 0.97       | 1.02  | 1.07  |  |  |  |

| b      | 0.35       |       | 0.43  |  |  |  |

| С      | 0.23       |       | 0.32  |  |  |  |

| D      | 10.20      | 10.30 | 10.40 |  |  |  |

| Е      | 10.10      | 10.30 | 10.50 |  |  |  |

| E1     | 7.40       | 7.50  | 7.60  |  |  |  |

| е      | 1.27 bsc   |       |       |  |  |  |

| L1     | 1.40 bsc   |       |       |  |  |  |

| L      | 0.55       |       | 0.85  |  |  |  |

| Y      |            | 0.10  |       |  |  |  |

| θ      | 0°         |       | 8°    |  |  |  |

NOTES

1.0 COPLANARITY APPLIES TO LEADS, CORNER LEADS AND DIE ATTACH PAD.

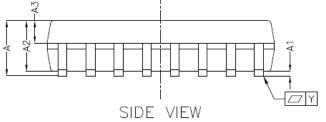

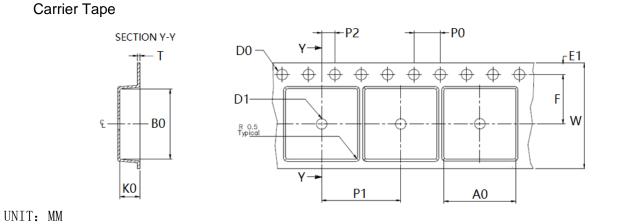

# 12 Tape and Reel Dimensions, SOIC16 Wide-Body

| PACKAGE     | A0    | B0    | K0   | D0         | D1    | W     | E1   | F    | P0   | P1    | P2   | Т     |

|-------------|-------|-------|------|------------|-------|-------|------|------|------|-------|------|-------|

| SOIC16      | 10.90 | 10.70 | 3.00 | Ø1.55      | Ø1.60 | 16.00 | 1.75 | 7.50 | 4.00 | 12.00 | 2.00 | 0.30  |

| (Wide-Body) | ±0.1  | ±0.1  | ±0.1 | $\pm 0.05$ | ±0.1  | ±0.3  | ±0.1 | ±0.1 | ±0.1 | ±0.1  | ±0.1 | ±0.05 |

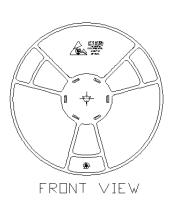

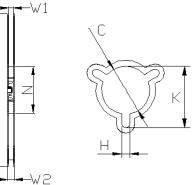

REEL

UNIT: MM

| TAPE SIZE | A    | Ν    | W1      | W2      | С     | К          | Н         |

|-----------|------|------|---------|---------|-------|------------|-----------|

| 16 MM     | Ø330 | Ø100 | 16.4    | 20.6    | Ø13.1 | 16.76      | 2.1       |

|           | ± 2  | ±2   | +2 / -0 | +2 / -0 | ± 0.2 | + 0.2 / -0 | +0.2 / -0 |

$\triangleleft$

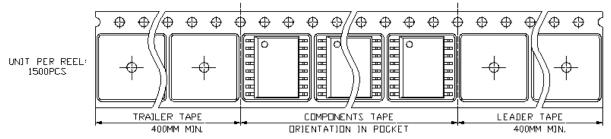

# TAPE

Leader / Trailer & Orientation

# **Revision History**

| Version | Date      | Subjects (major changes since previous revision)                                                                                                                                                                                                                                                        |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2021.8.3  | Initial datasheet available                                                                                                                                                                                                                                                                             |

| V1.1    | 2021.9.10 | <ol> <li>Delete "3.5A" from the title</li> <li>VDDL limit voltage upper limit is changed from 18V to 30V</li> <li>Delete CTI data items</li> <li>Delete the word "single" in the DTI data item</li> </ol>                                                                                               |

| V1.2    | 2022.3.23 | 1) Page 6 "Common mode transient immunity Logic High" &<br>"Common mode transient immunity Logic Low" is changed from<br>50 to 100, and the unit is changed from "kV/us" to "V/ns".                                                                                                                     |

|         |           | <ul> <li>2) Page 8 V<sub>ISO</sub> and V<sub>ISO_1s</sub> values update</li> <li>3) Page 4 add "Non-inverting driver input voltage" &amp; "Inverting driver input voltage", delete the word "(IP and IN)" in "Input-side logic levels"</li> <li>4) Page 14 Figure 9 "Tdeast_BLANKING" update</li> </ul> |